# Characterization of near-interface border-traps in GeO<sub>2</sub>/Ge gate stacks grown by thermal oxidation using deep-level transient spectroscopy

Wei-Chen Wen, <sup>1</sup> Keisuke Yamamoto, <sup>1</sup> Dong Wang <sup>1</sup> and Hiroshi Nakashima <sup>2</sup>

<sup>1</sup>Interdisciplinary Graduate School of Engineering, Kyushu University

<sup>2</sup>Global Innovation Center, Kyushu University

Kasuga-koen, Kasuga, Fukuoka 816-8580, Japan,

### **Abstract**

We developed a method for characterizing the near-interface border-traps (BTs) in GeO<sub>2</sub>/Ge gate stacks using deep-level transient spectroscopy. The BT density ( $N_{\rm BT}$ ) in p-MOS grown by low temperature oxidation is smaller than that by high temperature oxidation. By contrast, the  $N_{\rm BT}$  in n-MOS is almost the same regardless of the oxidation temperature. In addition, the  $N_{\rm BT}$  in p-MOS is drastically decreased by Al post metallization annealing (Al-PMA), but the  $N_{\rm BT}$  in n-MOS is not decreased. These results suggest that the species of BT in n-MOS are different from that of p-MOS.

#### 1. Introduction

A high-quality gate-stack formation on Ge is essential for high-performance Ge MOSFETs. Although a GeO2 is effective in reducing the interface-traps (ITs), a large amount of border-traps (BTs) causes serious problems. In this study, we established a method of BT characterization by deep-level transient spectroscopy (DLTS), investigated BTs in two kinds of MOS capacitors (CAPs) with a structure of SiO<sub>2</sub>/GeO<sub>2</sub>/Ge. One was a relatively thick GeO<sub>2</sub> by thermal oxidation at 550°C, at which GeO<sub>2</sub> volatilization may occur at the GeO<sub>2</sub>/Ge interface.<sup>[1]</sup> The other was a thin GeO<sub>2</sub> by the oxidation at 425°C, at which the volatilization may not occur. The Al post metallization annealing (PMA) effect on BT passivation was also studied.

### 2. Experimental

After substrate cleaning, 1 nm-SiO<sub>2</sub>/1 nm-GeO<sub>2</sub> bilayer passivation was performed  $^{[2]}$ , followed by a post thermal oxidation (PTO) at 550°C for 15 min or 425°C for 9 h in O<sub>2</sub> ambient. Next, 14-nm-thick SiO<sub>2</sub> was deposited on the both samples, followed by a post deposition annealing at 400°C for 30 min in N<sub>2</sub>. Then, an Al gate film was deposited on the SiO<sub>2</sub> surface by thermal evaporation. Before electrodes formation, an

optional Al-PMA was carried out at  $300^{\circ}$ C for 30 min in N<sub>2</sub>. The equivalent oxide thicknesses (EOTs) of the MOSCAPs with PTO at 550 and 425°C were ~19.5 and 16.8 nm, corresponding to GeO<sub>2</sub> thicknesses of 6.6 and 2.6 nm, respectively.

DLTS measurements were performed using a lock-in integrator. Pulse frequency f=10 Hz were used, which corresponds to BT position  $z_0=1.4$  nm from the interface for p-MOS and  $z_0=2.0$  nm for n-MOS.

### 3. Results and disscussion

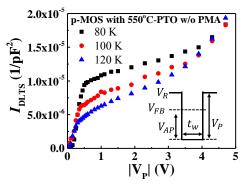

Fig. 1  $I_{DLTS}$  dependence on  $V_P$  for a p-MOS with PTO at 550°C without Al-PMA.

Figure 1 shows DLTS signal intensity ( $I_{DLTS}$ ) dependence on pulse height ( $V_P$ ) with a maximum pulse width ( $t_w$ ) of 5 ms at different temperatures ( $T_S$ ) for a MOSCAP with PTO at 550°C and without Al-PMA.

Let us pick up the result at 80 K as an example. The  $I_{DLTS}$  drastically increased when the  $V_P$  increased from 0 to 0.5 V. Note 0.5 V is approximately the  $V_{\rm FB}$  at 80 K for this sample. Therefore, this increase is dominated by the capture process of IT.[3] We believe that the weakest injection condition ( $t_w$ =2  $\mu$ s) under pulse intensity  $E_{AP}=0$  MV/cm is enough to compose the IT signals.  $(E_{AP} = V_{AP}/EOT$ , where  $V_{AP}$  is the applied voltage above flat band voltage.) Therefore, we use these data for IT density  $(D_{it})$  calculation. In the case of  $V_P > 0.5 \text{ V}$ , namely after the accumulation was established, the increase in  $I_{DLTS}$  with  $V_P >$ 0.5 V was governed by the capture process of BT because of an increase in hole numbers at Ge side of the GeO<sub>2</sub>/Ge interface. After subtracting the IT signal from  $I_{DLTS}$ , we calculate the BT density  $(N_{\rm bt})$ . The details of which will be presented in the forum.

$D_{\rm it}$  characteristics (not shown) are almost identical for both the MOSCAPs, implying that the interface property is not influenced by  ${\rm GeO_2}$  volatilization. The Al-PMA is effective in decreasing  $D_{\rm it}$  near the valence band edge but not near the conduction band edge (even worse), which is consistent with our previous experimental results of Al-PMA effects on Ge-MOSFET performance.<sup>[3, 4]</sup>

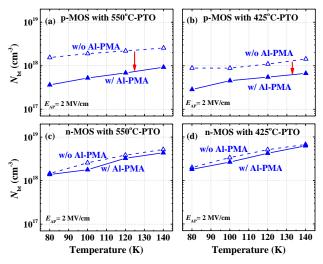

Figures 2(a) and 2(b) show dependence of  $N_{bt}$  on T for p-MOSCAPs with PTO at 550 and 425°C, respectively. Figures 2(c) and 2(d) represent the similar results for n-MOSCAPs with PTO at 550 and 425°C, respectively. It was confirmed from these results that 1) the  $N_{\rm bt}$  for p-MOS with is a half of 425°C-PTO that with 550°C-PTO under  $E_{AP}=2$ MV/cm, suggesting BT in p-MOS is associated with  $GeO_2$  volatilization; 2) the  $N_{bt}$  for p-MOS is drastically decreased by Al-PMA. The  $N_{\rm bt}$ s for n-MOS with PTO at 425 and 550°C (not shown) are almost the same and not decreased by Al-PMA, suggesting species of BT in n-MOS are different from that of p-MOS.

#### 5. Conclusion

Near-interface BT in GeO<sub>2</sub>/Ge structures were characterized by DLTS. The  $N_{\rm bt}$  in p-MOS were drastically decreased by Al-PMA, but the  $N_{\rm bt}$  in n-MOS was not decreased. This is a reason for difficulty of the electron mobility enhancement.

**Fig. 2** Dependence of  $N_{bt}$  on T for p-MOS with (a) 550°C-PTO and (b) 425°C-PTO. Dependence of  $N_{bt}$  on T for n-MOS with (c) 550°C-PTO and (d) 425°C-PTO. The results with Al-PMA are also shown.

## Acknowledgment

This study was partially supported by (JSPS) KAKENHI (Grant No. 26289090).

# Reference

- [1] K. Prabhakaran, F. Maeda, Y. Watanabe, T. Ogino, *Thin Solid Films* **2000**, 369, 289.

- [2] K. Hirayama, K. Yoshino, R. Ueno, Y. Iwamura, H. Yang, D. Wang, H. Nakashima, Solid State Electron. 2011, 60, 122.

- [3] D. Wang, S. Kojima, K. Sakamoto, K. Yamamoto, H. Nakashima, *J. of Appl. Phys.* 2012, 112, 083707.

- [4] Y. Nagatomi, T. Tateyama, S. Tanaka, W.C. Wen, T. Sakaguchi, K. Yamamoto, L. Zhao, D. Wang, H. Nakashima, *Mater. Sci. Semicond. Process.* 2017, 70, 246.

Email: 3ES17010E@s.kyushu-u.ac.jp